Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:36.

- Zadnja promjena 2025-01-23 14:47.

Cilj ovog projekta je stvoriti funkcionalnost prikaza slike pametnog zrcala. Ogledalo može prikazati prognoze (sunčano, djelomično sunčano, oblačno, vjetrovito, kiša, grmljavina i snijeg) i vrijednosti temperature od -9999 ° do 9999 °. Vrijednosti prognoze i temperature teško su kodirane kao da oponašaju njihovo raščlanjivanje iz vremenskog API -ja.

Projekt koristi ploču Zynq-Zybo-7000 sa FreeRTOS-om i koristi Vivado 2018.2 za projektiranje i programiranje hardvera.

Dijelovi:

Zynq-Zybo-7000 (sa FreeRTOS-om)

19 LCD (640x480)

VGA kabel

12 "x 18" ogledalo od akrila

Korak 1: Konfiguriranje Vivada

Preuzmite Vivado 2018.2 s Xilinxa i koristite licencu Webpack. Pokrenite Vivado i "Create New Project" i dajte mu ime. Zatim odaberite "RTL Project" i označite "Ne navodite izvore trenutno". Prilikom odabira dijela odaberite "xc7z010clg400-1" i pritisnite "Završi" na sljedećoj stranici.

Korak 2: Pakiranje IP -a VGA upravljačkog programa

Dodajte datoteku vga_driver.sv u izvore dizajna. Zatim kliknite "Alati" i odaberite "Kreiraj i pakiraj novi IP". Odaberite "Pakirajte svoj trenutni projekt". Zatim odaberite IP mjesto i "Uključi.xci datoteke." Na skočnom prozoru kliknite "U redu", a zatim "Završi".

Na stranici "Koraci pakiranja" idite na "Pregled i paket" i odaberite "Paket IP".

Sada bi vga_driver trebao biti dostupan kao IP blok.

Korak 3: Zynq IP

U odjeljku "IP Integrator" odaberite "Create Block Design". Dodajte "ZYNQ7 Processing System" i dvaput kliknite blok. Kliknite "Uvezi postavke XPS -a" i prenesite datoteku ZYBO_zynq_def.xml.

Zatim, pod "PS-PL Configuration" otvorite padajući izbornik za "AXI Non Secure Enablement" i označite "M AXI GP0 interface".

Zatim, pod "MIO konfiguracija" otvorite padajući izbornik "Procesorska jedinica aplikacije" i označite "Timer 0" i "Watchdog".

Na kraju, pod "Konfiguracija sata" otvorite padajući izbornik za "PL Fabric Clocks" i označite "FCLK_CLK0" na 100 MHz.

Korak 4: GPIO IP

Dizajnu blokova dodajte dva GPIO bloka. GPIO -i će se koristiti za kontrolu adrese piksela i RGB komponenti piksela. Konfigurirajte blokove kako je prikazano na gornjim slikama. Nakon što dodate i konfigurirate oba bloka, kliknite "Pokreni automatizaciju veze".

GPIO 0 - Kanal 1 kontrolira adresu piksela, a kanal 2 kontrolira crvenu boju.

GPIO 1 - Kanal 1 kontrolira zelenu boju, a kanal 2 kontrolira plavu boju.

Korak 5: Blokirajte memoriju

Dodajte Block Memory Generator IP u Block Design i konfigurirajte kao što je prikazano gore. Boje piksela se zapisuju na memorijske adrese koje zatim čita VGA upravljački program. Redak adrese mora odgovarati količini piksela koji se koriste, tako da mora biti 16 bita. Podaci su također 16 bita budući da postoji 16 bitova u boji. Ne marimo za čitanje bitova za potvrdu.

Korak 6: Ostali IP

U priloženom pdf -u prikazan je dovršeni dizajn bloka. Dodajte IP koji nedostaje i dovršite povezivanje. Također "Make Externals" za VGA izlaze u boji te vertikalne i horizontalne izlaze za sinkronizaciju.

xlconcat_0 - Povezuje pojedinačne boje u jedan 16 -bitni RGB signal koji se unosi u blok RAM.

xlconcat_1 - Povezuje signale stupaca i redaka iz VGA pogonitelja i dovodi se u port B blok RAM -a. To omogućuje VGA upravljačkom programu čitanje vrijednosti boje piksela.

VDD - konstanta HIGH spojena na omogućavanje pisanja blok RAM -a, tako da uvijek imamo pravo na to.

xlslice_0, 1, 2 - Kriške se koriste za razbijanje RGB signala na pojedinačne R, G i B signale koji se mogu unositi u VGA upravljački program.

Nakon što je dizajn bloka dovršen, generirajte HDL omot i dodajte datoteku ograničenja.

*Block Design temelji se na vodiču koji je napisao benlin1994*

Korak 7: SDK

Kôd koji pokreće ovaj Block Design nalazi se u nastavku. Init.c sadrži funkcije koje rukuju crtežom (predviđanja, brojevi, simbol stupnja itd.). Glavna petlja u main.c je ono što se pokreće kada je ploča programirana. Ova petlja postavlja vrijednosti predviđanja i temperature, a zatim poziva funkcije crtanja u init.c. Trenutno se petlja kroz svih sedam predviđanja i prikazuje jednu za drugom. Preporučuje se da u redak 239 dodate točku prekida kako biste mogli vidjeti svaku sliku. Kôd je komentiran i pružit će vam više informacija.

Korak 8: Zaključak

Kako bi se poboljšao trenutni projekt, mogle bi se učitati slike predviđanja unaprijed učitavanja u obliku COE datoteka u Block Memory Generators. Dakle, umjesto da ručno crtamo prognoze kao što smo to radili u C kodu, moglo bi se pročitati slike. Pokušali smo to učiniti, ali nismo uspjeli. Uspjeli smo pročitati vrijednosti piksela i ispisati ih, ali stvorili su neuredne slike koje nisu bile ništa poput onih koje smo prenijeli u RAM. Tehnički list Generator blok memorije koristan je za čitanje.

Projekt je u biti napola pametno ogledalo jer mu nedostaje aspekt internetske povezanosti. Dodavanjem ovoga dobilo bi se potpuno pametno ogledalo.

Preporučeni:

Napravite beskonačni zrcalni sat: 15 koraka (sa slikama)

Napravite beskonačni zrcalni sat: U prethodnom projektu izgradio sam beskonačno ogledalo, gdje mi je krajnji cilj bio pretvoriti ga u sat. (Napravite šareno ogledalo beskonačnosti) Nisam se time bavio nakon izgradnje jer, iako je izgledalo super, bilo je nekoliko stvari s tim

TTGO (kolor) zaslon s mikropythonom (TTGO T-zaslon): 6 koraka

TTGO (kolor) zaslon s Micropythonom (TTGO T-zaslon): TTGO T-zaslon je ploča temeljena na ESP32 koja uključuje zaslon u boji od 1,14 inča. Ploča se može kupiti za nagradu manju od 7 USD (uključujući dostavu, nagrada viđena na banggood -u). To je nevjerojatna nagrada za ESP32 uključujući zaslon. T

Jednostavan DIY beskonačni zrcalni sat: 3 koraka

Jednostavan DIY Infinity ogledalni sat: Ako vam je dosadno sa svojim normalnim satom, pokušajte napraviti ovaj cool DIY Infinity Mirror sat. Za poravnavanje vaše sobe

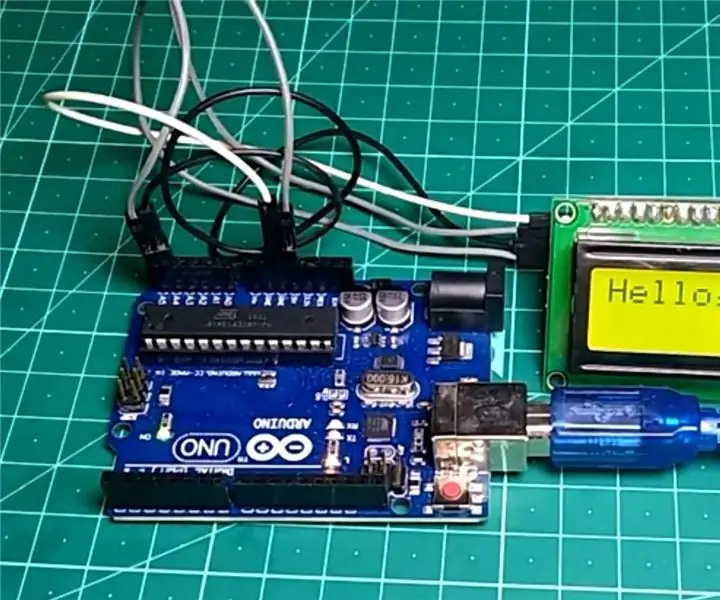

I2C / IIC LCD zaslon - Upotrijebite SPI LCD za I2C LCD zaslon Korištenje SPI do IIC modula s Arduinom: 5 koraka

I2C / IIC LCD zaslon | Upotrijebite SPI LCD na I2C LCD zaslonu Korištenje SPI na IIC modula s Arduinom: Zdravo dečki, budući da normalni SPI LCD 1602 ima previše žica za povezivanje pa je vrlo teško povezati ga s arduinom, ali na tržištu postoji jedan modul koji može pretvoriti SPI zaslon u IIC zaslon pa morate spojiti samo 4 žice

Beskonačni zrcalni sat: 5 koraka (sa slikama)

Infinity Mirror Clock: Ovo je ručno izrađen sat uglavnom za dekoraciju. U satu ima nekoliko LED svjetiljki, kada je uključen, to je prekrasan ukras za spavaću sobu. Kad je isključeno, to je malo ogledalo. Naravno, to je sam sat