Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:33.

- Zadnja promjena 2025-01-23 14:47.

Autor AmCoderhttps://www.linkedin.com/in/mituFollow Više od autora:

O: Mitu Raj - samo hobist i učenik - dizajner čipova - programer softvera - entuzijast fizike i matematike Više o AmCoderu »

## Ovo je najpopularnija i najpopularnija veza u Googleu za VHDL implementaciju CORDIC ALGORITHM -a za generiranje sinusnog i kosinusnog vala ## Trenutno postoje mnogi hardverski učinkoviti algoritmi, ali oni nisu dobro poznati zbog dominacije softverskih sustava nad mnogo godina. CORDIC je takav algoritam koji nije ništa drugo nego skup logika pomaka i dodavanja koji se koriste za računanje širokog raspona funkcija, uključujući određene trigonometrijske, hiperboličke, linearne i logaritamske funkcije. Ovo je algoritam koji se koristi u kalkulatorima itd. Dakle, samo pomoću jednostavnih mjenjača i zbrojeva možemo dizajnirati hardver manje složenosti, ali snage DSP -a pomoću kordičkog algoritma. Stoga se može dizajnirati kao goli RTL dizajn u VHDL -u ili Verilogu bez upotrebe namjenskih jedinica s pomičnim zarezom ili složenih matematičkih IP adresa.

Korak 1: VHDL i Modelsim

Ovdje je kordični algoritam implementiran pomoću VHDL -a za generiranje sinusnog i kosinskog vala. Može izvesti sinus i kosinus ulaznog kuta s velikom preciznošću. Kod se može sintetizirati na FPGA. Modelsim se koristi za simulaciju dizajna i ispitnog stola.

Korak 2: VHDL kôd za dizajn i ispitnu klupu

Binarna tehnika skaliranja koristi se za predstavljanje brojeva s pomičnim zarezom.

Prije kodiranja proučite priložene dokumente.

Prođite kroz stimulaciju cordic_v4.vhd - Dizajn - Ulaz je kut u 32 bita + predznak; može obraditi bilo koji kut od 0 do +/- 360 stupnjeva s preciznošću unosa 0,000000000233 stupnja. Pri davanju ulaza -> MSB je predznak, a ostalih 32 bita predstavljaju veličinu. -Izlaz dizajna je njegov sinus i cos vrijednost u 16 bita + predznak.ie; s preciznošću 0,00001526. Imajte na umu da je izlaz prikazan u obliku komplimenta 2 ako je odgovarajuća sinusna ili cos vrijednost negativna. Simulacija testb.vhd - Testna ploča za dizajn (1) Ulazni kutovi i povlačenje na povlačenje = '0'. Nakon dva koraka simulacije povucite resetiranje na '1' i "pokreni sve". (2) U prozoru simulacije postavite radiks sin i cos signala kao decimalni i format> Analogni (automatski). (3) Umanjite prikaz da biste vidjeli valni oblik pravilno.

Korak 3: Priložene datoteke

(1) cordic_v4.vhd - Dizajn. (2) testb.vhd - Ispitni sto za projektiranje.

(3) Dokument o tome kako forsirati kutne unose i pretvoriti binarne rezultate.

Ažuriranje: OVI DATOTEKE NISU DOSTAVLJENE I NE DOSTAVLJAJU SE VIŠE. MOLIMO VAS KORISTITE DATOTEKE IZ SLJEDEĆEG KORAKA

Korak 4: Mini -Cordic IP jezgra - 16 bita

Ograničenje gornje implementacije je spora, niža radna frekvencija zbog izračunavanja u jednom ciklusu takta. Mini-Cordic IP Core- 16 Bit

- Kritični putevi raspoređeni u više ciklusa radi poboljšanja performansi.- Brže- FPGA provjereni dizajn sintetiziran do takta od 100 Mhz.- Više područja optimizirano u HDL-u, Manji hardver.- Dodani signali statusa učitavanja i gotovog stanja.- Jedina mana je manja rezolucija u odnosu na prethodni. Testbench:

potpuno automatizirani od 0 do 360 stupnjeva

Priložene datoteke: 1) mini kabelska glavna vhdl datoteka2) mini kabelska ispitna klupa3) Mini Cordic IP Core priručnik4) Doc o tome kako forsirati kutove i pretvoriti rezultate

Za sve upite, slobodno me kontaktirajte:

Mitu Raj

pratite me:

mail: iammituraj@gmail.com

### Ukupno preuzimanja: 325 do 01.05.2021 ###

### Zadnja izmjena koda: srpanj-07-2020 ###

Preporučeni:

Samobalansirajući robot - PID kontrolni algoritam: 3 koraka

Self Balancing Robot - PID Control Algorithm: Ovaj je projekt zamišljen jer me zanimalo saznati više o upravljačkim algoritmima i kako učinkovito implementirati funkcionalne PID petlje. Projekt je još uvijek u fazi razvoja jer se Bluetooth modul tek treba dodati što će omogućiti

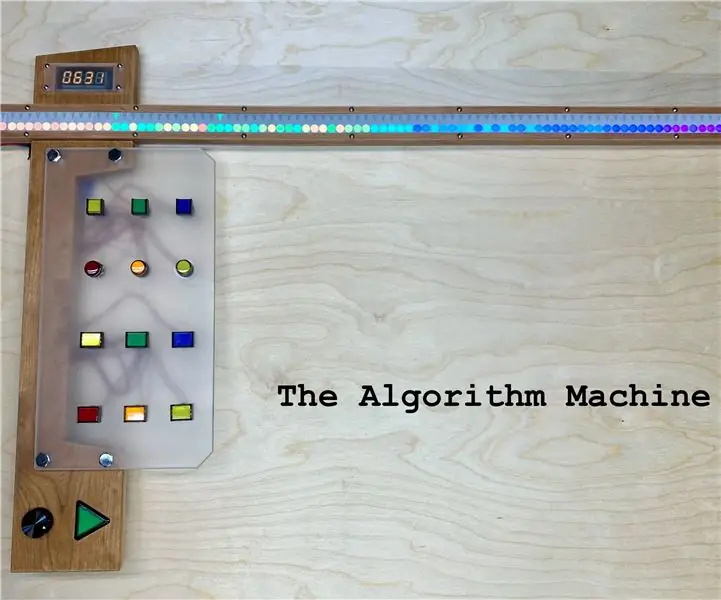

Stroj za algoritam: 13 koraka (sa slikama)

Stroj za algoritme: Predajem informatiku na fakultetu 15 godina, i iako je moja stručnost više na strani programiranja, i dalje provodim dosta vremena pokrivajući standardne algoritme za pretraživanje i sortiranje. S nastavnog stajališta

Umjetna inteligencija za društvene igre: minimalni algoritam: 8 koraka

Umjetna inteligencija za društvene igre: Minimaksni algoritam: Jeste li se ikada zapitali kako nastaju računala protiv kojih igrate u šahu ili damu? Pa ne tražite dalje od ovog Instructablea jer će vam pokazati kako napraviti jednostavnu, ali učinkovitu umjetnu inteligenciju (AI) koristeći Minimax algoritam! Korištenjem th

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: 9 koraka

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: Dobro došli u uputstva o tome kako izgraditi štopericu koristeći osnovnu VHDL i Basys 3 ploču. Drago nam je što možemo podijeliti naš projekt s vama! Ovo je bio posljednji projekt za tečaj CPE 133 (digitalni dizajn) na Cal Polyu, SLO u jesen 2016. Projekt koji smo izgradili

Tic Tac Toe na Arduinu s AI (minimalni algoritam): 3 koraka

Tic Tac Toe na Arduinu s AI (Minimax Algoritam): U ovom Instructable -u ću vam pokazati kako izgraditi Tic Tac Toe igru s AI -om pomoću Arduina. Možete igrati protiv Arduina ili gledati Arduino kako igra protiv sebe. Koristim algoritam zvan "minimaksni algoritam"