Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:32.

- Zadnja promjena 2025-01-23 14:47.

JDM je popularan PIC programer jer koristi serijski port, minimalni broj komponenti i ne zahtijeva napajanje. No, postoji zabuna, s mnogim varijacijama programera na internetu, koje rade s kojim PIC -ovima? U ovom "instruktivnom" testiranju stavljamo JDM na test i ja pokazujem kako simulirati sklop pomoću Spicea koji će odgovoriti na sva vaša pitanja!

Pribor

LTspice koji se ovdje mogu preuzeti s Analog Devices.

Ovdje su vam potrebne i datoteke JDM kola.

Korak 1: Zahtjevi za serijski port

JDM zahtijeva serijski port koji zadovoljava specifikacije EIA232, idealno s +12/-12 razinama napona.

Prema podatkovnom listu Texas Instruments Line Driver MC1488 (slika 3)

Izlazna impedancija = 4V/8mA = 500 ohma.

Ograničenje struje kratkog spoja = 12mV, bez vremenskog ograničenja - bez oštećenja čipa.

Preporučuje se ulazna impedancija linijskog prijemnika = 3k do 7k ohma.

Serijski portovi na starijim stolnim računalima koriste +12v/-12V koji ispunjavaju ovaj zahtjev.

Serijski priključci na novijim prijenosnim računalima koriste niže napone. JDM može, ali i ne mora raditi - odgovor je složeniji.

Korak 2: Zahtjevi programiranja PIC -a

Informacije o zahtjevima programiranja PIC -a dobivaju se od Microchipa. Gore navedeno odnosi se na tipičan uređaj.

Korak 3: JDM specifikacija

Je li izvorno JDM web mjesto izgubljeno u magli vremena? To nas ostavlja nagađanjem što je dizajner izvorno namjeravao za specifikaciju.

- Omogućite VDD = 5V i najviše do IDD = 2mA (za verziju "u utičnici")

- Omogućite VHH = 13V, a do IHH = 0,2 mA maksimalno.

- MCLR Vrijeme porasta tVHHR = 1uS max.

- ICSP verzija mora biti u stanju povući MCLR nisko u odnosu na povlačenje od 22 k na meti.

Korak 4: Opis kruga

Slika JDM1 temelji se na "standardnom" JDM krugu preuzetom s web stranice PICPgm. Ovo je programer “PIC in Socket” gdje PIC preuzima napajanje sa TX i RTS pinova. Izvorni dijagram je bilo teško razumjeti pa sam ga precrtao koristeći uobičajenu konvenciju protoka struje od vrha do dna. Dodao sam LED indikatore "RESET", "PROG" i "RTS" koji su potrebni tijekom izgradnje i ispitivanja. Nadajmo se da oni nemaju štetan učinak na ponašanje.

Uobičajena konvencija dizajna kruga zajednička je za sve osnove, ali ključna značajka JDM -a je to što je uzemljenje serijskog porta (GND) spojeno na VDD. To stvara zabunu jer se signali serijskog porta mjere u odnosu na GND, PIC signali u odnosu na logičko tlo (VSS).

Kad TX poraste, Q1 se ponaša kao dvije diode prema naprijed. (Kolektor Q1 nije obrnuto pristran kao kod normalnog rada tranzistora). Q1 kolektor puni C2, koji je stegnut na VDD+8V od strane Zenera (D3). Odašiljač Q1 isporučuje 13V MCLR -u za Program/Verify Mode.

Kad TX padne, kondenzator C3 se puni kroz D1, a VSS se stegne na VDD-5V pomoću zenera (D5). Također TX je stegnut na (VSS-0,6) pomoću D1. Q1 je isključen, C1 zadržava punjenje za sljedeći programski impuls. MCLR je stegnut na 0V pomoću D2, pa je PIC sada resetiran.

Kad je RTS visok, sat se prenosi na PGC. D4 stezaljka PGC na VDD logici visoka. Kad je RTS nizak, kondenzator C3 se puni kroz D6 i VSS se stegne na VDD-5V pomoću zenera (D5). D6 steže PGC na VSS ili logičkom 0.

Tijekom programiranja, podaci poslani na DTR čitaju se na PGD -u, koji PIC konfigurira kao ulaz. Kad je DTR visok, Q2 djeluje kao "sljedbenik emitera", a napon PGD-a je oko (VDD-0,6) ili logika 1. Kad je DTR nizak, Q2 djeluje kao loš tranzistor (obrnuti pinovi emitera i kolektora). Q2 povlači PGD nisko, što je stegnuto D7 na VSS ili logičkoj 0.

Tijekom provjere PIC konfigurira PGD kao izlaz za slanje podataka na serijski port. DTR mora biti postavljen visoko, a podaci se čitaju na CTS -u. Kad je izlaz PGD visok, Q2 je isključen, CTS = DTR = +12V. Kad je izlaz PGD nizak, uključen je Q2. Q2 kolektor crpi struju (12V+5V)/(1k+1k5) = 7mA iz DTR -a i povlači CTS nisko, do VSS -a.

Korak 5: Pripremite se za simulaciju

Preuzmite LT spice, spremite i otvorite datoteke kruga (*.asc) ovdje navedene. Da bismo simulirali krug, moramo mu dati neke ulaze, a zatim "pratiti" izlaze. V1, V2 V3 simuliraju 12V serijski port s izlaznom impedansom R11, R12, R13.

- V1 generira 2 programska impulsa na TX -u od 0,5 ms do 4,5 ms

- V2 generira niz podatkovnih impulsa na DTR -u od 1,5 do 4,5 ms

- V3 generira niz taktova na RTS -u od 0,5 do 3,5 ms

Komponente V4, X1, R15 i R16 dio su simulacije.

- V4 generira 2 impulsa od 2,5 do 4,5 ms za provjeru podataka.

- Jumper X1 simulira OUTPUT na PGD -u.

- R15, R16 simuliraju "učitavanje" PIC -a na VDD i MCLR.

Korak 6: Izmjene za ICSP

Slika JDM3 prikazuje inačicu programiranja "u krugu". Izmjene u odnosu na izvornik su

- Zip utičnicu zamijenite ICSP konektorom.

- PIC se sada napaja opskrbom ciljnog kruga (V5).

- Uklonite 5V zener (D5).

- Mali kondenzator od 100 pF (C4) pomiče se pored PIC -a na ciljnom krugu.

- LED diode napajaju ploču, gdje je to moguće.

- MCLR vučni otpornik (R10) i dioda (D10) potrebni su na ciljnom krugu.

- UPOZORENJE. Ciljna ploča mora imati "plutajući" izvor napajanja, idealno bateriju.

- Nemojte spajati ciljno uzemljenje (VSS) na masu računala/računala povezivanjem bilo kojih drugih računarskih portova istovremeno s JDM -om.

Nakon simulacije JDM1, problem dugog vremena punjenja na C2 postao je očit. Zatim se nakon čitanja Fruttenboela čini da su C2 i Q1 dodani kao izmjena izvorniku. Ne mogu misliti što C2 i Q1 namjeravaju učiniti osim stvaranja problema. Stoga se za JDM4 vraćamo na stariji dizajn na Fruttenboelu koji je jednostavan i jasan za razumjeti. D1 i D3/LED2 stezaljka MCLR između VSS i VDD+8V. Vrijednost R1 je smanjena na 3k3, taman toliko da se LED2 osvijetli na 12V.

JDM4 je također dizajniran za rad sa slabijim serijskim portovima. Kad TX poraste (+9V), izvor struje TX = (9-8)/(1k +3k3) = 0,2 mA, tek toliko da se MCLR podigne visoko, iako nedovoljno za osvjetljavanje LED2. Kad TX padne (oko -7V), TX struja potone = (9-7)/1k = 2mA. LED1 struja = (7-2 za LED)/(2k7) = 1,8 mA. MCLR povlačna struja = 7-5,5/3k3 = 0,5 mA.

Ovaj krug je također testiran (simulacija JDM5) kako bi se vidjelo što se događa sa serijskim portovima +/- 7V minimum, gdje nema dovoljno napona za održavanje VHH = 13V. Svrha C1 sada postaje očita, C1 stvara kratko +ve pojačanje MCLR -a, skok od 33us na rastućem rubu TX -a, dovoljno dugo da PIC uđe u programski način, možda? No uklonite kratkospojnik X2 (onemogućite LED1) jer nema dovoljno struje da se MCLR povuče na nisko i zajedno osvijetli LED1. Kad TX padne, TX struja pada = (7V-5.5V)/(1k+3k3) = 0.3mA, taman toliko da se MCLR povuče nisko u odnosu na pull-up R10.

Korak 7: Rezultati simulacije

Za pregled grafičkih datoteka, bolje je da desnom tipkom miša kliknete donje veze, a zatim odaberete "Otvori vezu na novoj kartici"

Simulacija 1: trag MCLR -a, VSS -a i RTS -a za izvorni JDM1. Odmah su uočljiva zapažanja 1, 2 i 3.

Simulacija 2: trag MCLR -a i VSS -a i RTS -a za modificirani JDM2, koji rješava prethodne probleme.

Simulacija 3: trag PGD -a, VSS -a i PGC -a za JDM2 slanje podataka u programskom načinu rada. Promatranje 4 na 3,5 mS.

Simulacija 4: trag PGD -a, VSS -a i CTS -a za JDM2 u načinu provjere (umetnut kratkospojnik X1). u redu

Simulacija 5: trag MCLR -a, VSS -a, PGD -a i PGC -a za JDM3. ICSP pomoću napajanja iz kruga rješava mnoge probleme.

Simulacija 6: trag MCLR-a, VSS-a, PGD-a i PGC-a za JDM4 s +/- 9V serijskim portom. MCLR odmah raste, potpuno radi.

Simulacija 7: trag MCLR-a, VSS-a i TX-a za JDM5 s uklonjenim serijskim portom +/- 7V i kratkospojnikom X2. C1 stvara +ve pojačanje (šiljak) na rastućem rubu MCLR -a, otprilike dovoljno za pomicanje MCLR -a iznad TX -a na 13V.

Korak 8: Zaključci

Spice je zaista dobar u otkrivanju "skrivenih tajni" rada kruga. Očigledno JDM krug radi i kompatibilan je s mnogim PIC čipovima, ali sljedeća zapažanja otkrivaju moguća ograničenja/probleme s kompatibilnošću/greške?

- Dugo vrijeme porasta MCLR -a dok se C2 puni do VPP -a pri prvom impulsu TX -a. Ne uspijeva specifikacija 3.

- Serijski port puni C2 kada TX poraste, a RTS padne. No, RTS ima i posao punjenja C3. Kada se oboje dogodi u isto vrijeme, to stvara veće opterećenje za RTS, posljedično C3 gubi naboj (VSS raste) pri 2 ms pri simulaciji. Ne uspijeva specifikacija 1.

- C3 gubi naboj (VSS počinje rasti) nakon što taktni impulsi prestanu na 3,5 ms.

- Koja je svrha C2, je li uopće potreban?

Rješenja

- Vjerojatno PICPgm koristi softverski „radni krug“. Mora primijeniti dugi TX impuls za prednabijanje C2, a zatim ući u način programiranja tek nakon drugog TX impulsa? Za simulaciju sam smanjio vrijednost C2 na 1uF do vremena uspona od 1 ms. Nije idealno rješenje.

- Podijelite C2 i C3 pa se pune neovisno. Jedna mala izmjena JDM2, C2 upućuje na GND umjesto na VSS.

- Riješio JDM3. ICSP je mnogo pouzdaniji jer PIC pokreće ciljno kolo.

- JDM4 rješava problem 1. Ovo je jednostavan dizajn koji potpuno eliminira C2.

Korak 9: I na kraju

Dokaz pudinga je u jedenju. Ovaj JDM radi pa ga nastavite koristiti.

A moje preporuke su:

- koristite JDM2 za programiranje utičnica i 12V serijske portove,

- koristite JDM4 za ICSP programer i serijske portove iznad +/- 9V,

- koristite JDM4 sa uklonjenim kratkospojnikom X2 za serijske portove iznad +/- 7V.

Reference:

Začin Analog Devices LT

picpgm

Fruttenboel

Pratite još PIC projekata na lukavom uglu

Preporučeni:

Elegoo Super Started Kit Uno R3 Pregled: 4 koraka

Elegoo Super Started Kit Uno R3 Pregled: Prije nekoliko dana Elegoo mi je poslao ovaj Super Starter Kit na testiranje. Pa da vidimo što se nalazi unutra. Otvaranjem ovog kompaktnog kućišta možemo vidjeti mnogo toga. Na naslovnici se nalazi indeks sa svim komponentama. Unutra imamo zahvalnicu sa svim s

BGA RTG pregled- naučite kako pregledati?: 7 koraka

BGA X-Ray Inspection-Saznajte kako pregledati?: Ovaj Instructable će vas naučiti kako pripremiti upotrebu i 2D x-ray sustav za pregled BGA-e, kao i neke savjete na što trebate paziti prilikom obavljanja BGA X-Ray pregleda trebat će: rentgenski sustav sposoban držati PCBPCBESD smockESD narukvicu za zglob

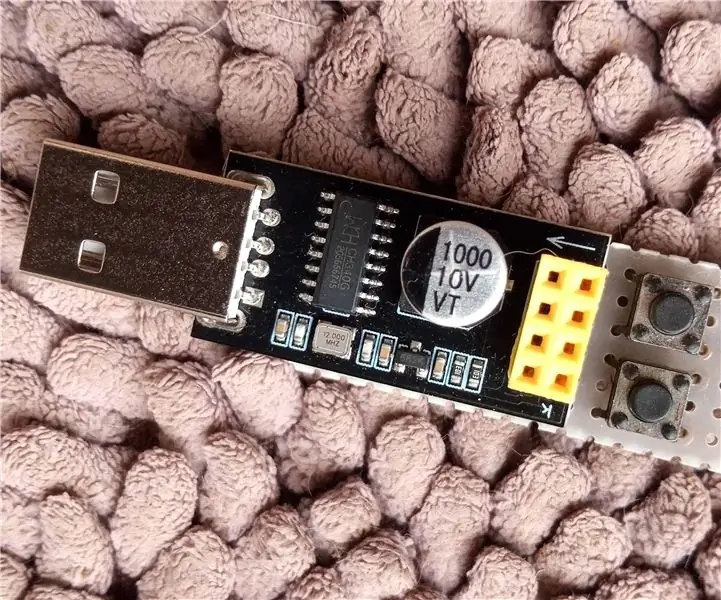

Hakiranje programera ESP -01 - Jednostavno :): 6 koraka

Hack programatora ESP-01-The Easy One :): Zdravo ESPers, U ovom uputstvu pokazat ću vam jednostavan hack za izradu programera za modul ESP-01 / ESP8266-01 / ES-01. Većina nas je koristila Arduino ploču ili FTDI USB-TTL uređaje kao programere za ovaj modul. Obje metode dobro funkcioniraju. Ali t

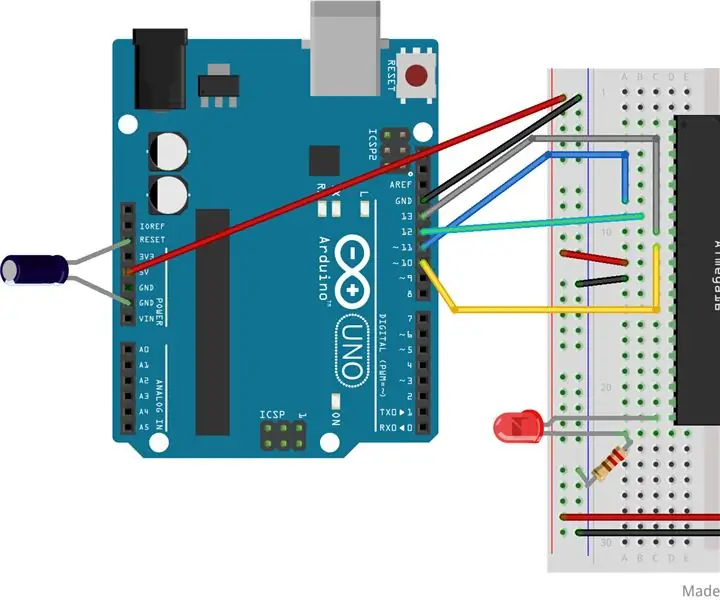

Kako prenijeti C kod na ِ AVR pomoću programa Arduino Uno kao programera: 6 koraka

Kako prenijeti C kod na ِ AVR pomoću programa Arduino Uno kao programera: Pozdrav svima: D Ovdje ću podijeliti jednostavan način programiranja bilo kojeg AVR čipa pomoću Arduino Uno R3 Sve što trebate snimiti kod na svoj mikrokontroler je Arduino Uno umjesto da kupujete određene programer koji košta puno

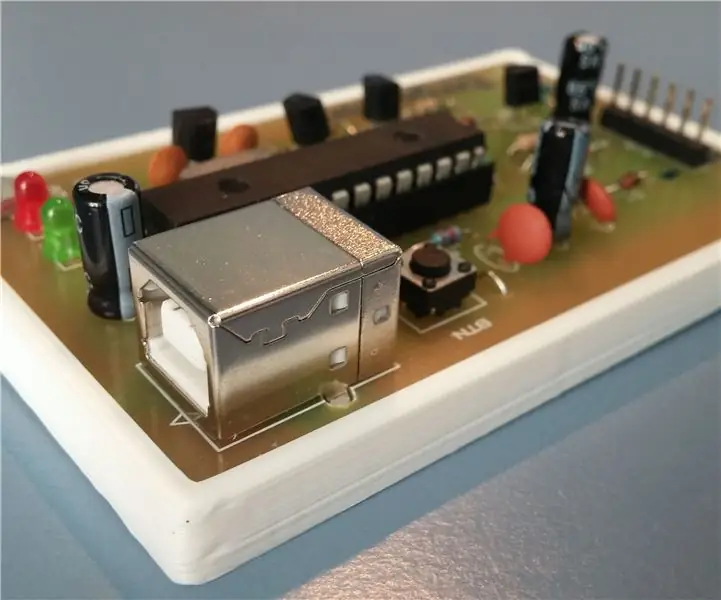

Kako napraviti PIC programera - PicKit 2 'klon': 4 koraka (sa slikama)

Kako napraviti PIC programera - PicKit 2 'klon': Bok! Ovo je kratki Instructable o izradi PIC programera koji djeluje kao PicKit 2. Ovo sam napravio jer je mnogo jeftiniji od kupnje originalnog PicKita i zato što Microchip, proizvođači PIC mikrokontrolera i PicKit programer, pr