Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:34.

- Zadnja promjena 2025-01-23 14:47.

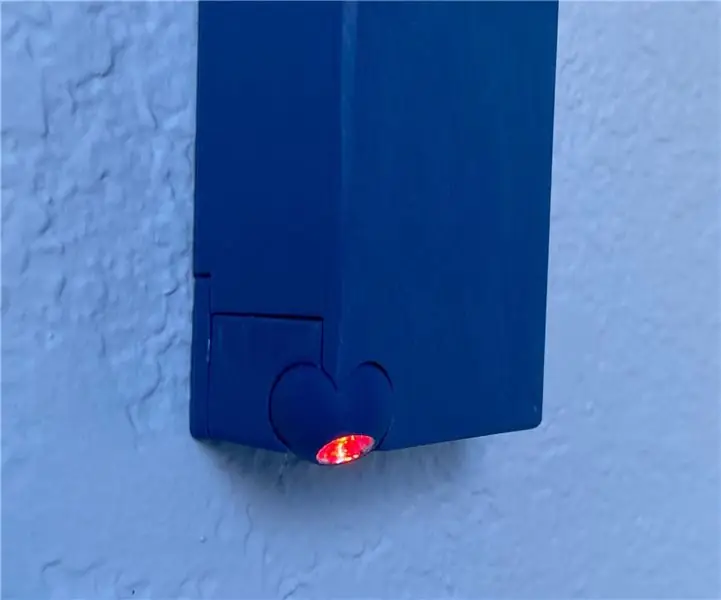

Naš cilj s ovim projektom bio je stvoriti nešto što će zajednicama uštedjeti energiju i financijske resurse. Ulična svjetla koja se aktiviraju pokretom učinila bi obje ove stvari. Širom zemlje energija se troši na ulična svjetla koja osvjetljavaju prazne ulice. Naš sustav uličnog osvjetljenja osigurava da svjetla budu uključena samo kada je to potrebno, čime se zajednicama štedi bezbroj dolara. Pomoću senzora pokreta sustav uključuje svjetla samo kada su prisutni automobili. Također zbog sigurnosti pješaka, implementirali smo gumb za poništavanje koji uključuje sva svjetla na ulici. Sljedeći koraci će vas provesti kroz to kako smo osmislili i izgradili naš smanjeni model projekta koristeći Vivado i Basys 3 ploču.

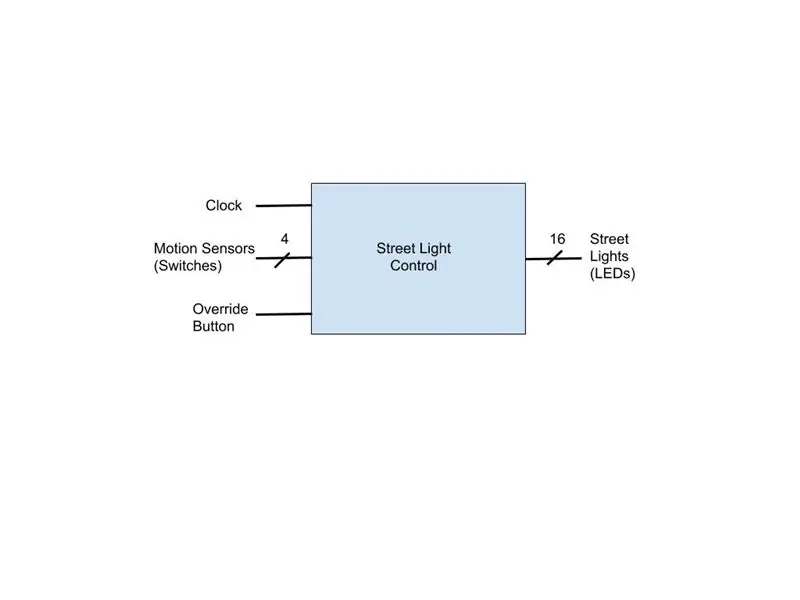

Korak 1: Sistemska crna kutija

Ovaj smo projekt započeli crtanjem jednostavnog dijagrama crne kutije. Dijagram u crnoj kutiji jednostavno prikazuje ulaze i izlaze koji su potrebni našem sustavu za dovršetak svih potrebnih procesa. Pokušali smo zadržati što jednostavniji i osnovni dizajn. Naša tri ulaza u sustav uključivala su sabirnicu senzora pokreta (4 za naš smanjeni model), gumb za premošćavanje pješaka i ulaz za sat. S druge strane, naš jedini izlaz je sabirnica LED svjetala koja predstavljaju naša ulična svjetla. Za ovaj model koristili smo scenarij od 16 uličnih svjetiljki jednostavno zato što je to najveći broj ugrađenih LED izlaza na ploči Basys 3. Konačno, pomoću ovog dijagrama uspjeli smo stvoriti naš projekt Vivado, datoteke izvora i ograničenja s odgovarajućim ulazima i izlazima.

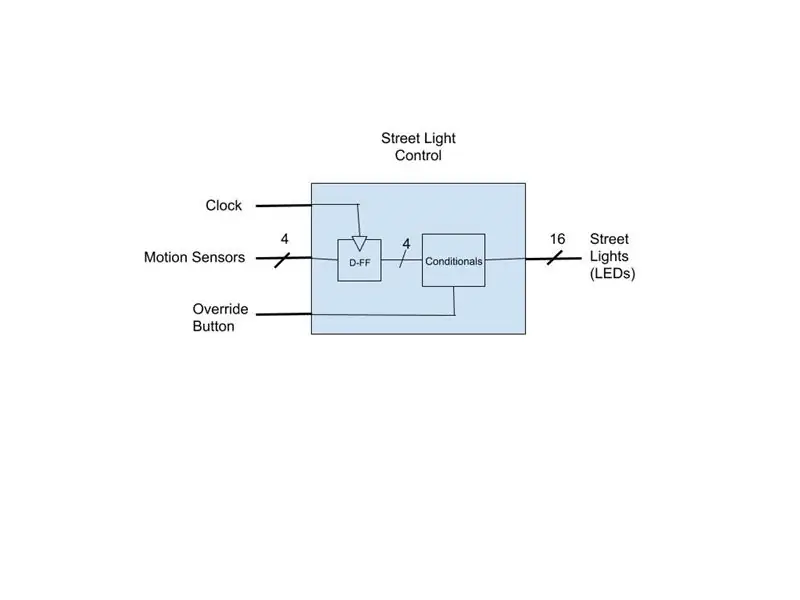

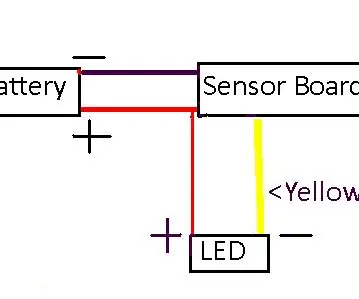

Korak 2: Komponente

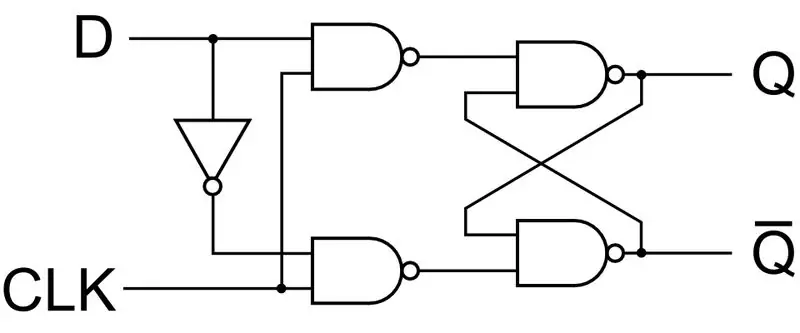

U ovom koraku dublje istražujemo komponente koje čine naš dijagram crne kutije. Naša prva komponenta je izvorna datoteka VHDL koja sadrži D japanke. D japanke jednostavno prihvaćaju bilo koji signal koji im se šalje sa senzora na rastućem rubu sata, i hvataju te podatke do sljedećeg rastućeg ruba. To sprječava naše osjetljive senzore pokreta da izazovu "treperenje" izlaznih LED dioda. Također, stavljamo jedan D flip-flop na ulazni signal gumba da LED diode ostanu uključene oko 5-7 sekundi nakon pritiska na gumb. Ovo smo također proveli kroz razdjelnik sata.

entitet clk_div2 je Port (clk: u std_logic; sclk: van std_logic); kraj clk_div2;

arhitektura my_clk_div od clk_div2 je

konstanta max_count: cijeli broj: = (300000000); signal tmp_clk: std_logic: = '0'; započeti my_div: process (clk, tmp_clk) varijabla div_cnt: integer: = 0; start if (rise_edge (clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; završi ako; završi ako; sclk <= tmp_clk; završi proces my_div; kraj my_clk_div;

Naša posljednja komponenta u ovom dijagramu je izvorna VHDL datoteka ponašanja koja sadrži uvjete za izlaze temeljene na konfiguraciji ulaznih signala.

Korak 3: D Japanke

Četiri japanke priključene na ulazne signale bitne su za funkcionalnost našeg sustava. Kao što je ranije rečeno, s osjetljivim senzorima pokreta i tipkom za poništavanje, japanke koriste zasune samo za izlaz našeg ulaznog signala na rastućem rubu sata. Ova sekvencijalna logika znači da naša ulična svjetla mogu ostati uključena određeno vrijeme nakon što se aktiviraju brzim pokretom. Kodiranje D-japanke prilično je jednostavno:

beginprocess (CLK) begin ako rise_edge (CLK) tada je Q <= D; završi ako; završetak procesa;

Cijela se stvar može sastaviti u jednu if naredbu. Nakon što smo imali ovaj komad, stvorili smo strukturnu VHDL izvornu datoteku koja sadrži sva četiri naša potrebna japanka:

započeti DFF0: mapa porta DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: Mapa porta DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Mapa DFF portova (CLK => CLK, D => D (2), Q => Q (2)); DFF3: karta DFF portova (CLK => CLK, D => D (3), Q => Q (3));

kraj Ponašanje;

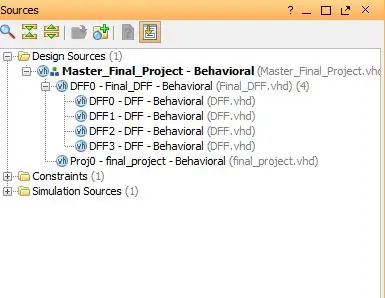

To pomaže u održavanju naše glavne strukturne datoteke u kojoj okupljamo sve komponente sustava mnogo čistijim i organiziranijim.

Korak 4: Uvjeti

Kako bi naš kôd bio kompaktan i učinkovit, napisali smo sve uvjete u jednu izjavu slučaja. Za naš smanjeni model imali smo 16 mogućih LED izlaznih konfiguracija jer je svaki senzor pokreta odgovoran za skupinu od 4 LED diode.:

slučaj NMS je kada je "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; završni slučaj;

Korak 5: Ograničenja

Da biste ispravno naveli svoje ulaze i izlaze koristeći Vivado, morate implementirati datoteku ograničenja koja navodi sve priključke, gumbe, LED diode i satove koji se koriste.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [1]} PACK U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W18 get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN {14 [get] LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_ports {LED 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] IO set_property STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] set_property IOS33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVCMOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [1P} PAGE] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Korak 6: Glavna izvorna datoteka

U ovoj glavnoj datoteci okupljamo sve prethodno spomenute izvorne datoteke komponenti. Ova datoteka funkcionira kao strukturni kod koji okuplja različite komponente.

entitet Master_Final_Project je Port (BTN: u STD_LOGIC; CLK: u STD_LOGIC; MS: u STD_LOGIC_VECTOR (3 do 0); LED: van STD_LOGIC_VECTOR (15 do 0)); kraj Master_Final_Project;

arhitektura Ponašanje Master_Final_Project je

komponenta final_project je port (--CLK: u STD_LOGIC; NMS: u STD_LOGIC_VECTOR (3 do 0); BTN: u STD_LOGIC; --sw: u STD_LOGIC_Vector (1 do 0); LED: van STD_LOGIC_VECTOR (15 do 0); krajnja komponenta;

komponenta Final_DFF je

Port (CLK: u STD_LOGIC; D: u STD_LOGIC_Vector (3 do 0); Q: van STD_LOGIC_Vector (3 do 0)); krajnja komponenta;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

početi

DFF0: Finalna_DFF karta porta (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa porta final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); kraj Ponašanje;

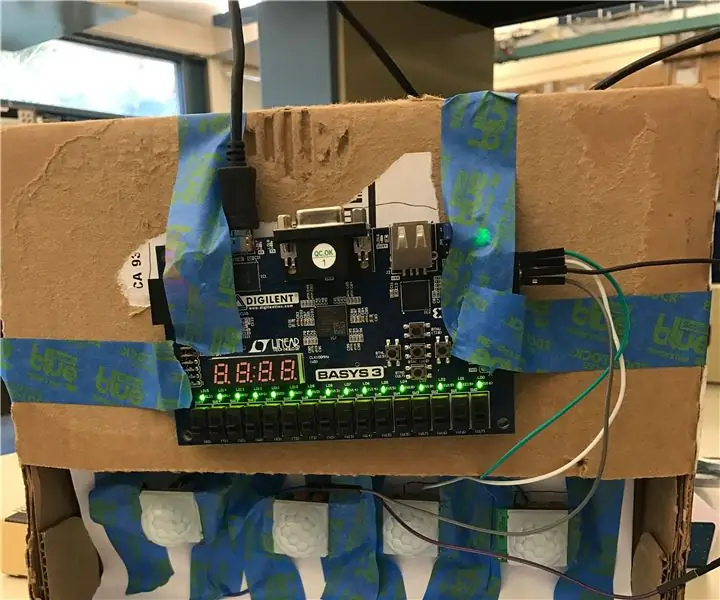

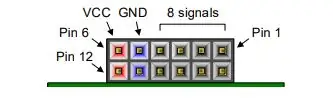

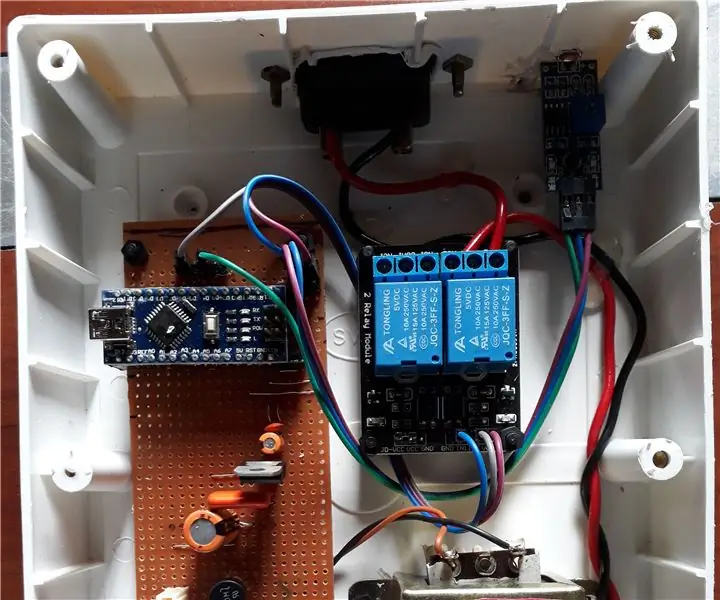

Korak 7: Montaža

Sklop hardvera za ovaj projekt je minimalan. Jedini potrebni komadi su sljedeći:

1. Ploča Basys 3 (1)

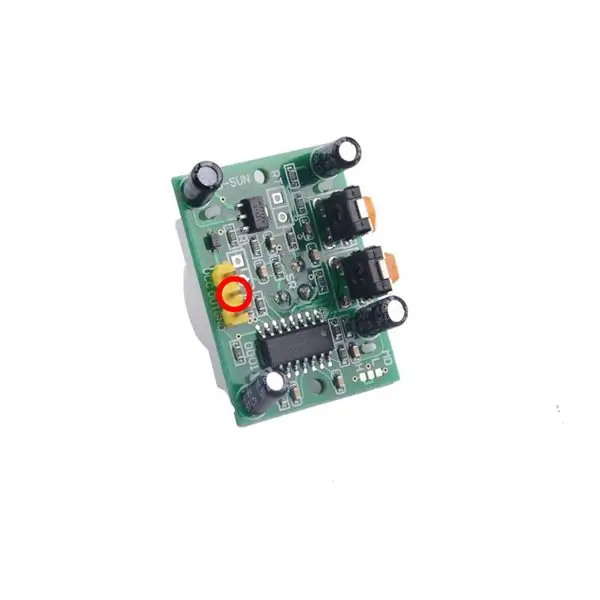

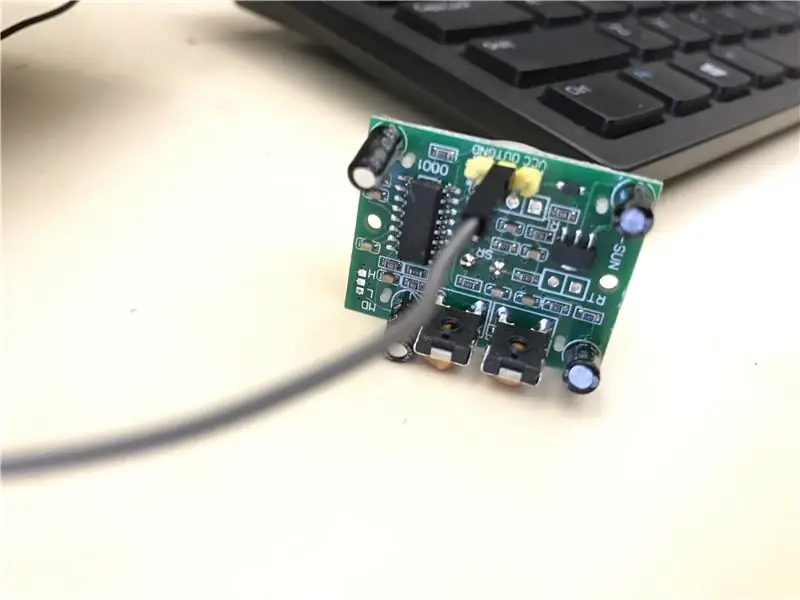

2. Jeftini senzori pokreta koji se na Amazonu mogu pronaći ovdje. (4)

3. Muški do ženski vodiči (4)

Skupština:

1. Spojite 4 muška kabela na priključke JB zaglavlja PMod 1-4 (vidi sliku).

2. Spojite ženske krajeve na svaki izlaz senzora pokreta.

Korak 8: Učitavanje programa

Sada smo spremni za učitavanje VHDL glavne izvorne datoteke na Basys 3 ploču. Pokrenite sintezu, implementaciju i generirajte provjeru protoka bitova za moguće greške. Ako se sve uspješno pokrene, otvorite upravitelj hardvera i programirajte uređaj Basys 3. Vaš je projekt sada dovršen!

Preporučeni:

Krila za cosplay pokretom aktivirana pomoću Circuit Playground Express - 1. dio: 7 koraka (sa slikama)

Krilca za igranje s pokretom aktivirana pomoću Circuit Playground Expressa - 1. dio: Ovo je prvi dio projekta u dva dijela, u kojem ću vam pokazati moj postupak izrade para automatiziranih vilinskih krila. Prvi dio projekta je mehaniku krila, a drugi dio čini ga nosivim i dodaje krila

Automatska ulična svjetla pomoću ultrazvučnog senzora: 3 koraka

Automatska ulična svjetla pomoću ultrazvučnog senzora: Jeste li ikada pomislili kako se ulična rasvjeta automatski uključuje noću, a ujutro se automatski isključuje? Postoji li netko tko želi uključiti/isključiti ova svjetla? Postoji nekoliko načina za uključivanje uličnih svjetala, ali sljedeći c

Ponovno ugradite zvučno aktivirana LED svjetla u Jukebox: 4 koraka

Nadograđivanje zvučno aktiviranih LED svjetala u Jukebox: Razmišljao sam o tome da napravim svjetla koja bi mijenjala boju s vremenom uz neku glazbu, da dodam u džuboks, neko vrijeme i kad sam vidio izazov za brzinu LED trake, a budući da smo trenutno u zatvoru, mislio sam da će ovo biti

LED lampa aktivirana pokretom na baterije: 4 koraka

LED lampa aktivirana pokretom pomoću baterije: Ako želite staviti svjetlo negdje koje se ne može spojiti, ovo je možda upravo ono što vam treba

Prekidač svjetla aktiviran pokretom sa senzorom svjetla: 5 koraka

Prekidač svjetla aktiviran pokretom sa senzorom svjetla: Prekidač svjetla aktiviran pokretom ima mnogo primjena kako u kući tako i u uredu. Ovo je, međutim, imalo dodatnu prednost uključivanjem svjetlosnog senzora, tako da se ovo svjetlo može aktivirati samo noću