Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:36.

- Zadnja promjena 2025-01-23 14:47.

Znam što mislite: "Huh? Postoji mnogo instrukcija o tome kako koristiti mikrokontrolere za mjerenje frekvencije signala. Zijevati." No, pričekajte, u ovome postoji novost: opisujem metodu mjerenja frekvencija mnogo veću nego što mikrokontroler (MCU) može podnijeti i radni ciklus signala - sve u isto vrijeme!

Frekvencijski raspon uređaja obuhvaća od ~ 43 Hz do ~ 450 kHz, dok se radni ciklus kreće od 1% do 99%.

Dopustite mi da objasnim dio "može podnijeti": MCU mjeri razdoblje signala kvadratnog vala, T, praćenjem vremena između dva slijedeća prijelazna događaja. Na primjer, niski do visoki napon skače na jedan od njegovih I/O pinova. To čini brojeći broj impulsa vlastitog unutarnjeg sata. Naivno, gornja granica za izmjerene frekvencije trebala bi biti u skladu s teoremom o uzorkovanju Nyqvist-Shannon; tj. otprilike bi bila jednaka polovici frekvencije takta MCU -a. U stvarnosti granica je mnogo, mnogo niža, jer MCU mora izvršiti kôd za obradu prekida, spremanje varijabli, izvršavanje aritmetičkih operacija, prikaz rezultata itd. U mojim pokusima s MCU -om od 48 MHz minimalni broj ciklusa takta između mjerljivih prijelaza bio je oko 106. Dakle, gornja granica mjerljivog frekvencijskog područja u ovom slučaju bila bi 48 000 /212 /2 = 226,4 kHz.

Dok MCU mjeri razdoblje signala, on također može odrediti njegovu širinu impulsa, P: vrijeme preostalog visokog napona signala. Drugim riječima, vrijeme između prijelaza od niskog do visokog i od visokog do niskog. Radni ciklus signala tada se definira kao sljedeći postotak:

Dužnost = 100% * P / T

Kao i u slučaju frekvencije, postoji praktično ograničenje širine impulsa. Koristeći gornji primjer, 106 ciklusa takta ograničilo bi širinu impulsa na najmanje 2,21 mikrosekundi. Ili, najmanje 50% na 226,4 kHz.

Jedan od načina povećanja gornje granice frekvencije signala pravokutnog vala je primjena digitalnih razdjelnika koji koriste japanke. Dijeljenje ulazne frekvencije s n produžilo bi mjerljivi gornji raspon n puta. Ovo je sjajna vijest, digitalni razdjelnici imaju jedan temeljni nedostatak: podijeljeni signal gubi informacije o širini impulsa (i radnom ciklusu)! Zbog načina rada razdjelnika njihov izlaz uvijek ima 50% radni ciklus. Sramota…

Na sljedećim stranicama pokazat ću kako digitalno podijeliti frekvenciju i sačuvati izvornu širinu impulsa što mi omogućuje mjerenje signala daleko izvan granica koje nameće izravno brojanje.

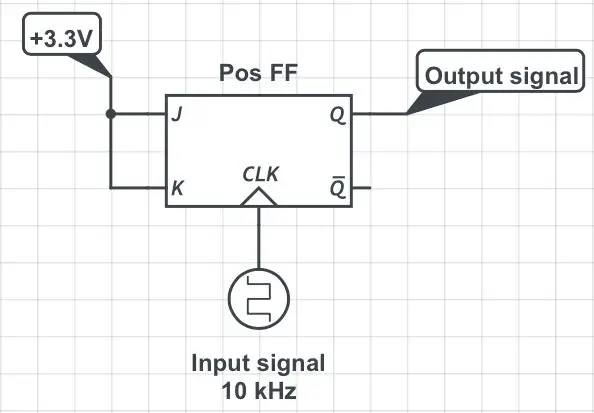

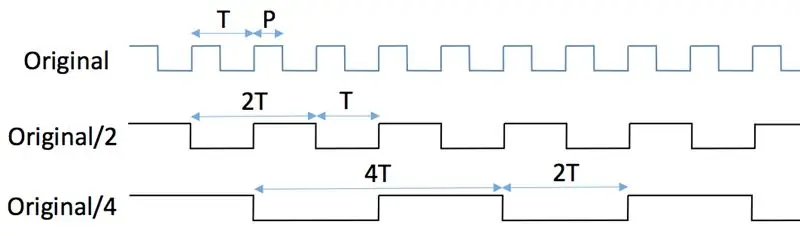

Korak 1: Podjela digitalnih frekvencija

Tradicionalni digitalni razdjelnici frekvencija koriste japanke; ovaj vodič lijepo objašnjava principe kako konstruirati razdjelnike koristeći standardne JK japanke. Time se rješava problem previsokih ulaznih frekvencija za MCU, ali ima jedan veliki nedostatak: podijeljeni signal ima 50% radni ciklus, bez obzira na dužnost ulaznog signala! Da biste vidjeli zašto je to tako, pogledajte prve dvije brojke. Izvorni signal s periodom T i širinom impulsa P dovodi se u iglu sata JK japanke, dok su njegovi pinovi J i K stalno držani visoko (prva slika). Logika 3.3V je cijela. Pretpostavimo da je japanka pokrenuta pozitivnim (tj. Rastućim) rubom sata. U tim uvjetima, promjene stanja izlaznog pina (pojedinačni "flips" i "flops") događaju se svaki put kada pin sata pređe s niskog na visoko. Prijelaz visoke na nisku vrijednost sata (tj. Negativni rub) potpuno se zanemaruje. Pogledajte drugu sliku. Izlazni pin, Q, emitira signal čije je razdoblje dvostruko duže od izvornog razdoblja, odnosno njegova se frekvencija prepolovi. Širina impulsa na izlazu uvijek je jednaka T. Zbog toga se gubi izvorna širina impulsa, P.

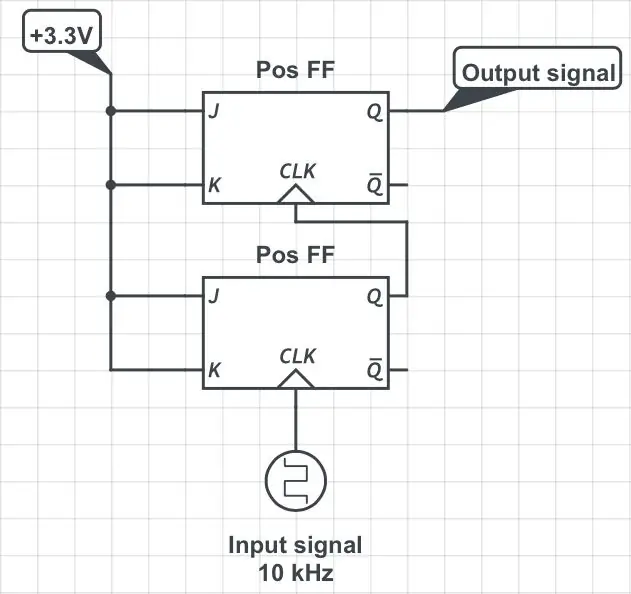

Dodavanjem još jednog JK japanke u konfiguraciji prikazanoj na trećoj slici, izvorna frekvencija se dijeli sa 4. Dodavanjem više japanki na isti sekvencijalni način frekvencija se dijeli na sljedeće snage 2: 8, 16, 32 itd.

Problem: kako podijeliti frekvenciju kvadratnog vala uz očuvanje njegove širine impulsa?

Ideja je pravilno dodati JK japanku s negativnim rubom pokrenutu u miks. Nazovimo to "Neg FF"; vidi četvrtu sliku. Ovdje "ispravno" znači da su J i K pinovi novih japanki vezani za Q i Qbar izlazne pinove razdjelnika-4 ("Pos FF") prikazanog na prethodnoj slici. (Ovdje je "traka" vodoravna traka iznad simbola Q koja označava logičku negaciju.) Da biste vidjeli što se time postiže, pogledajte tablicu funkcija "Neg FF" na petoj slici: Negovi izlazi, Q i Qbar, preslikavaju stanje svojih ulaznih pinova, J i K, respektivno. Što znači da odražavaju stanje Pos 'Q i Qbar. No, Negova flip-flop akcija mora pričekati negativni rub izvornog signala, koji stiže u vrijeme P nakon pozitivnog ruba. Aha!

Dobiveni valni oblici prikazani su na šestoj slici. "Pos Q" daje signal na 1/4 frekvencije, "Pos Qbar" je li inverzan, "Neg Q" slijedi "Pos Q" pomaknut za širinu impulsa P, a "Neg Qbar" je njegov inverzan. Možete provjeriti da logičko AND "Pos Qbar" i "Neg Q" proizvodi niz impulsa koji karakterizira izvorna širina impulsa P i 1/4 frekvencije. Bingo!

U početku sam koristio upravo ovaj izlazni signal za napajanje MCU -a. Međutim, pokazalo se da je problematično za vrlo kratke širine impulsa zbog ograničenja 106 ciklusa MCU -a spomenutog u uvodu. Ovaj mali problem riješio sam odabirom drugog izlaza: "Pos Qbar" I "Neg Qbar". Jedan pogled na valne oblike trebao bi vas uvjeriti da širina impulsa ovog određenog valnog oblika, P ', varira između T i 2T umjesto (0, T) raspona za P. P se može lako oporaviti iz P':

P = 2T - P '

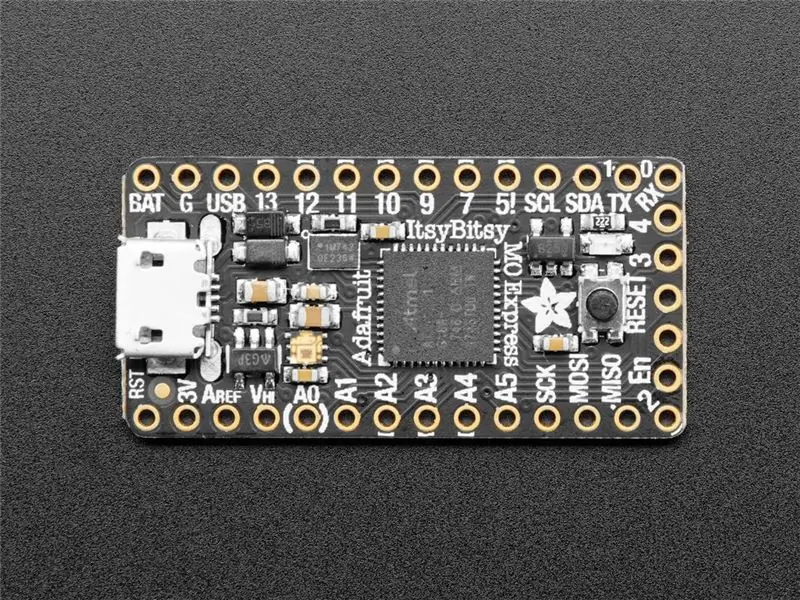

Korak 2: Preporučeni hardver

Zaista mi se sviđa relativni pridošlica u elektroničke hobiste: Atmel SAM D21 MCU-i temeljeni na 32-bitnom ARM Cortex M0+ procesoru koji radi na 48 MHz, što je mnogo više od starijih Atmela. Za ovaj projekt sam kupio:

- ItyBitsy M0 Express MCU ploča iz Adafruit -a

- Slučajno sam imao punjivu LiPo bateriju iz Adafruit -a

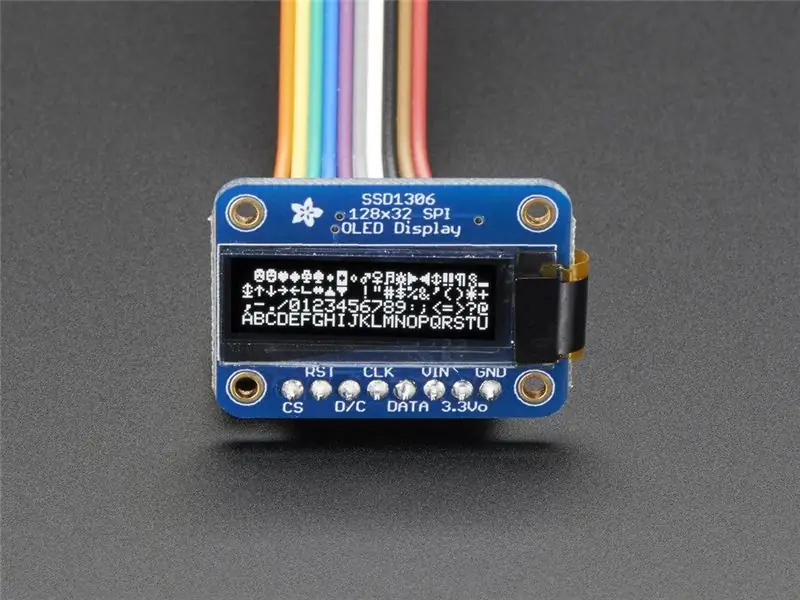

- Jednobojni 128x32 SPI OLED zaslon (pogađate: Adafruit)

- Dvostruki JK japanka s pozitivnim rubom SN74HC109 iz Texas Instruments

- Dvostruki JK flip-flop SN74HC112 s negativnim rubom okidača tvrtke Texas Instruments

- Četverostruki i kapija CD74AC08E iz Texas Instruments

- Četverostruki ili kapija CD74AC32E tvrtke Texas Instruments

Korak 3: Krug

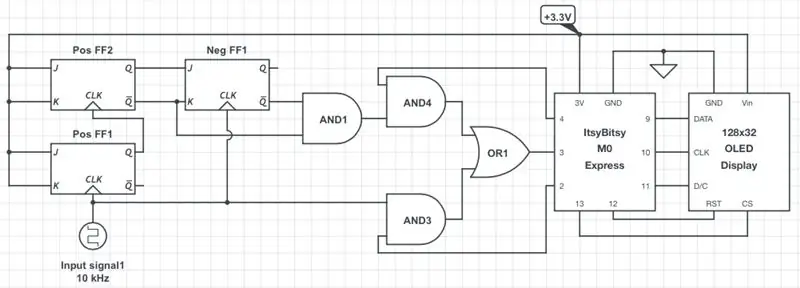

Prva slika prikazuje pojednostavljenu shemu mjerača frekvencije/radnog opterećenja. Čitavo se pretpostavlja CMOS logika od 3,3 V. Slijedom toga, amplituda ulaznog kvadratnog vala mora biti između odgovarajućeg VIH razine (tj. 2 V) i 3,3 V. Ako nije, morate je povećati ili smanjiti prema tome. U većini slučajeva bio bi dovoljan jednostavan razdjelnik napona. Ako želite dizajnirati svoju verziju mjerača na drugoj logičkoj razini, tada morate upotrijebiti drugi mikro upravljač (MCU), bateriju i zaslon koji rade na željenoj razini. Logička vrata i japanke korišteni u ovom projektu rade s logičkim razinama bilo gdje između 2 V i 6 V i u većini bi slučajeva trebali biti u redu.

Kao što je prikazano, ItsyBitsy MCU koristi pinove 9-13 za komunikaciju s zaslonom putem softverskog SPI protokola. 3V pin isporučuje napajanje cijelom krugu. Digitalni ulazni pin 3 prihvaća analizirani signal, dok pinovi 2 i 4 kontroliraju izvor signala: ili izravni signal koji dolazi kroz vrata AND3 (niske ulazne frekvencije), ili signal podijeljen s 4 kroz vrata AND4 (visoke ulazne frekvencije) kako je opisano u koraku 2 Kôd, o kojem će biti riječi u sljedećem koraku, automatski detektira dolazni raspon frekvencija i na odgovarajući način prebacuje izvor signala.

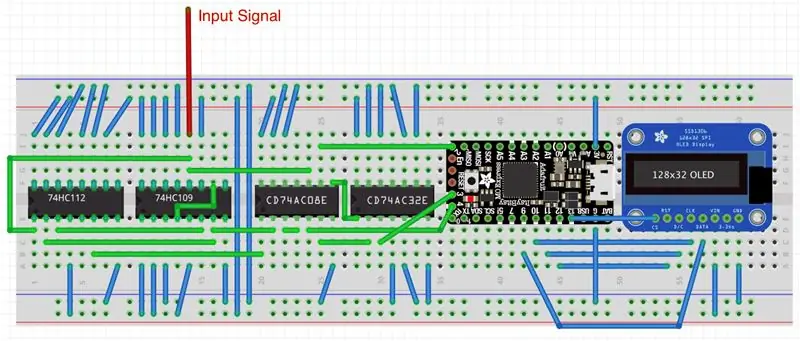

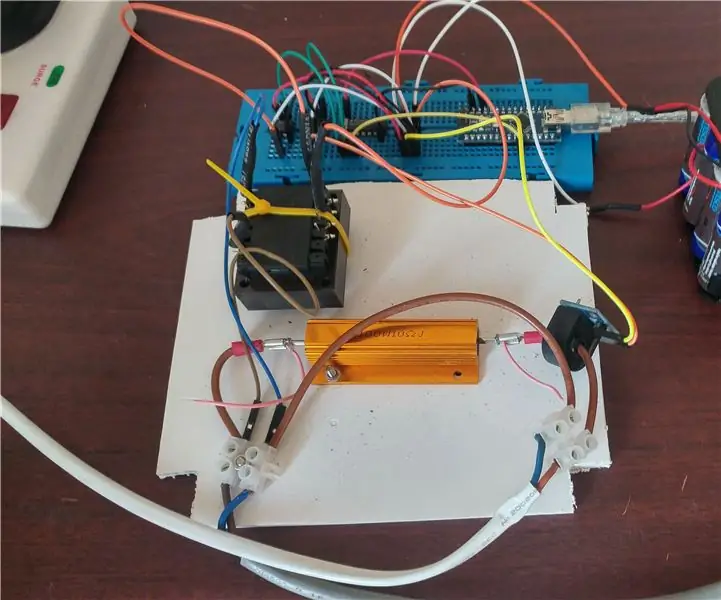

Shema ne prikazuje pravu složenost povezivanja digitalnih čipova. Druga slika prikazuje kako bi projekt izgledao na ploči. Ulazni signal dolazi kroz crvenu žicu do 2CLK pina dvostrukog flip-flopa s pozitivnim rubom. OPREZ: Obično bi sve J i K pinove ovog japanke trebalo držati visoko, ali SN74HC109 posebno sadrži Kbar pin - obrnuti K pin - umjesto toga. Dakle, ovaj pin mora biti uzemljen! Prvi flip-flop s negativnim rubom u SN74HC112 ima svoj 1K i 1J pin spojen na 1Q i 1Qbar pinove SN74HC109. Drugi japanka u SN74HC112 se ne koristi i njegovi ulazni pinovi (2K, 2J, 2CLRbar) su uzemljeni. Svi ostali dodatni pinovi PREbar (unaprijed postavljeni) i CLRbar (čisti) u svim japankama moraju biti povezani na logičko visoko. Neiskorišteni pinovi sata i izlaza ostaju nepovezani. Slično, neiskorišteni ulazni pinovi na svim vratima su uzemljeni, dok se neiskorišteni izlazi ostaju nepovezani. Kao što sam govorio u svom "Nevidljivom ubojici telefonskog prstena", uzemljenje neiskorištenih ulaznih pinova logičkih čipova uklanja slučajne oscilacije i štedi energiju baterije.

Korak 4: Kôd i mjerenje niskih frekvencija

Naravno, sve se radnje događaju u dolje navedenom kodu. Kad se ulazni ulaz na pin 3 prebaci s digitalnog niskog na visoko, MCU počinje brojati impulse svog unutarnjeg takta od 48 MHz. On bilježi trenutak prijelaza s visokog na nisko i nastavlja brojati do sljedećeg prekidača s niskog na visoko, kada ponovno pokreće cijeli proces. Prvi broj predstavlja širinu impulsa, dok cijeli broj predstavlja razdoblje signala. I to je cijela tajna.

CPU bilježi te prijelaze putem hardverskih prekida. SAMD21 ima nekoliko satova; moj kôd koristi TC3 one. U početku sam počeo čitajući tablicu podataka M0 koja je uložila napore za puno napora u kodiranju rukovatelja prekida, ali ubrzo sam otkrio vrlo povezan kod u postovima na Arduino forumu korisnika electro_95, MartinL i Rucus čiji je doprinos propisno priznato. Uključio sam i izmijenio njihov kombinirani kod u svoj; štedi mi puno vremena!

Kao što sam već spomenuo, razlučivost signala ograničena je sa ~ 106 CPU ciklusa za izvršavanje koda između prekida. Digitalna podjela sa očuvanjem širine impulsa brine se o visokim frekvencijama. S druge strane, niske frekvencije predstavljaju još jedan izazov: budući da je brojač sata TC3 dugačak 16 bita, prelijeva se nakon što pređe granicu od 65, 536 brojanja. Može se riješiti ova situacija dodavanjem prekida prelijevanja, ali je odabrano drugo rješenje: TC3 može koristiti unaprijed kalibriran (tj. Softverski podijeljen) CPU sat umjesto hardverskog 48 MHz. Stoga, ako se razdoblje signala približi granici prelijevanja, kôd može uputiti TC3 da koristi brojeve od 24 MHz za sljedeće razdoblje i, voila, brojač pada ispod 32, 768 točaka. Za još niže frekvencije, TC3 se može uputiti da broji impulse od 12 MHz itd. Odgovarajući predskaler automatski se određuje na temelju frekvencije signala, s histerezom, kako bi se brojač TC3 zadržao unutar granice prelijevanja. Kao rezultat toga, donji dio raspona uređaja je oko 43 Hz.

Možete kôd razdijeliti i upotrijebiti u svom projektu, ali navedite njegov izvor pri objavljivanju rezultata.

Veza na kôd.

Preporučeni:

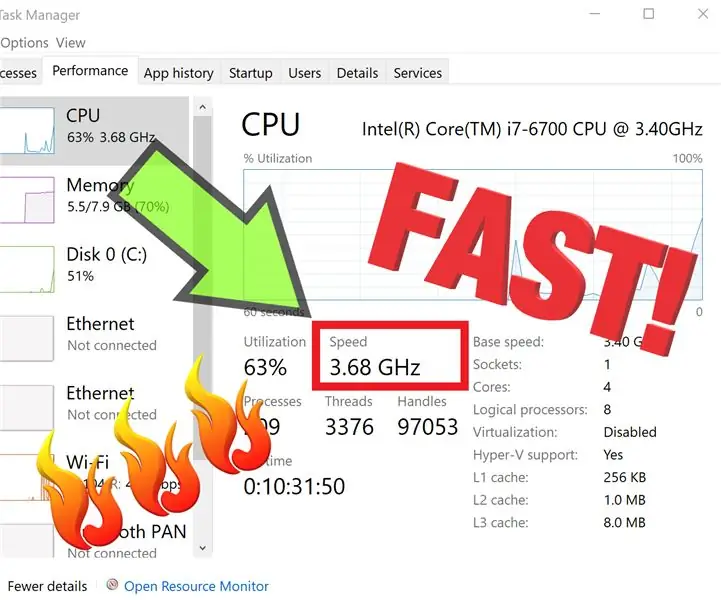

Kako prilagoditi frekvenciju procesora u sustavu Windows 10: 5 koraka

Kako prilagoditi frekvenciju procesora u sustavu Windows 10: Ovo pokazuje kako prilagoditi frekvenciju procesora, kao i usporavanje/ograničavanje ili otključavanje pune brzine CPU -a na vašem računalu sa sustavom Windows 10

Mjerite mrežnu frekvenciju pomoću Arduina: 7 koraka (sa slikama)

Izmjerite mrežnu frekvenciju pomoću Arduina: 3. travnja premijer Indije, Shri. Narendra Modi apelirao je na Indijance da isključe svjetla i zapale lampu (Diya) u 21:00 5. travnja u znak obilježavanja borbe Indije protiv korona virusa. Odmah nakon objave nastao je veliki kaos

Kako napraviti bespilotnu letjelicu pomoću Arduina UNO - Napravite četverokopter pomoću mikrokontrolera: 8 koraka (sa slikama)

Kako napraviti bespilotnu letjelicu pomoću Arduina UNO | Napravite četverokopter pomoću mikrokontrolera: Uvod Posjetite moj kanal na YouTubeu Drone je vrlo skup gadget (proizvod) za kupnju. U ovom postu ću raspravljati o tome kako to učiniti jeftino ?? I kako možete sami napraviti ovakav po povoljnoj cijeni … Pa u Indiji svi materijali (motori, ESC

Kako mjeriti faktor izmjenične struje pomoću Arduina: 4 koraka

Kako mjeriti faktor izmjenične struje pomoću Arduina: Pozdrav svima! Ovo je moje treće uputstvo, nadam se da će vam biti informativno :-) Ovo će biti uputstvo o tome kako napraviti osnovno mjerenje faktora snage pomoću Arduina. Prije nego počnemo, potrebno je imati na umu nekoliko stvari: Ovo će raditi SAMO sa

Alarm za visoku toplinu: 3 koraka

Alarm za visoku toplinu: Ovo je jednostavan alarm koji sam napravio kako bi se isključio kad temperatura u zamrzivaču ili drugom sličnom uređaju pređe određenu temperaturu u stupnjevima. Mislio sam da će to pomoći ako vam da malo naznake o tome