Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 09:33.

- Zadnja promjena 2025-01-23 14:47.

U ovom Instructable opisat ćemo kako implementirati 8-bitni analogno-digitalni pretvarač (ADC) u SLG46855V koji može osjetiti struju opterećenja i sučelje s MCU-om putem I2C. Ovaj se dizajn može koristiti za različite primjene mjerenja struje, kao što su ampermetri, sustavi za otkrivanje grešaka i mjerači goriva.

U nastavku smo opisali korake potrebne za razumijevanje načina na koji je rješenje programirano za stvaranje trenutnog smisla ADC -a. Međutim, ako samo želite dobiti rezultat programiranja, preuzmite GreenPAK softver kako biste vidjeli već dovršenu datoteku za dizajn GreenPAK. Priključite GreenPAK Development Kit na svoje računalo i udarite u program za stvaranje trenutnog smisla ADC -a.

Korak 1: ADC arhitektura

ADC se u osnovi sastoji od analognog usporednika i digitalno-analognog pretvarača (DAC). Usporednik osjeća ulazni napon u odnosu na izlazni napon DAC -a, a zatim kontrolira hoće li povećati ili smanjiti ulazni kod DAC -a, tako da izlaz DAC konvergira na ulazni napon. Rezultirajući DAC ulazni kod postaje ADC digitalni izlazni kod.

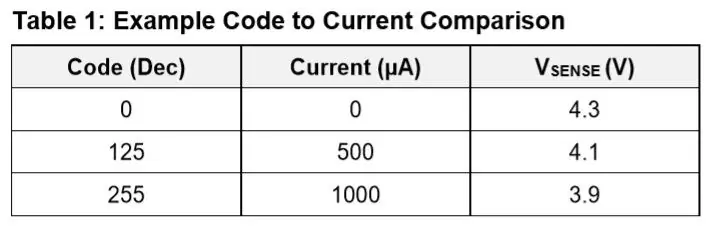

U našoj implementaciji stvaramo DAC pomoću mreže otpornika kontrolirane pulsno-širinskom modulacijom (PWM). Pomoću GreenPAK -a lako možemo stvoriti precizan digitalno upravljani PWM izlaz. PWM kad se filtrira postaje naš analogni napon i stoga služi kao učinkovit DAC. Izrazita prednost ovog pristupa je u tome što je lako postaviti napone koji odgovaraju nultom kodu i punoj ljestvici (ekvivalentno pomak i pojačanje) jednostavnim podešavanjem vrijednosti otpornika. Na primjer, korisnik želi idealno očitati nulti kôd s temperaturnog senzora bez struje (0 µA) koja odgovara 4,3 V, a kôd u punom opsegu na 1000 µA koji odgovara 3,9 V (tablica 1). To se lako provodi jednostavnim postavljanjem nekoliko vrijednosti otpornika. Budući da se raspon ADC -a podudara s rasponom senzora koji nas zanima, maksimalno koristimo ADC rezoluciju.

Dizajn razmatranja ove arhitekture je da unutarnja frekvencija PWM -a mora biti mnogo brža od brzine ažuriranja ADC -a kako bi se spriječilo nedovoljno prilagođeno ponašanje njegove upravljačke petlje. U najmanju ruku trebao bi biti dulji od takta brojača podataka ADC -a podijeljenog s 256. U ovom dizajnu razdoblje ažuriranja ADC -a postavljeno je na 1,3312 ms.

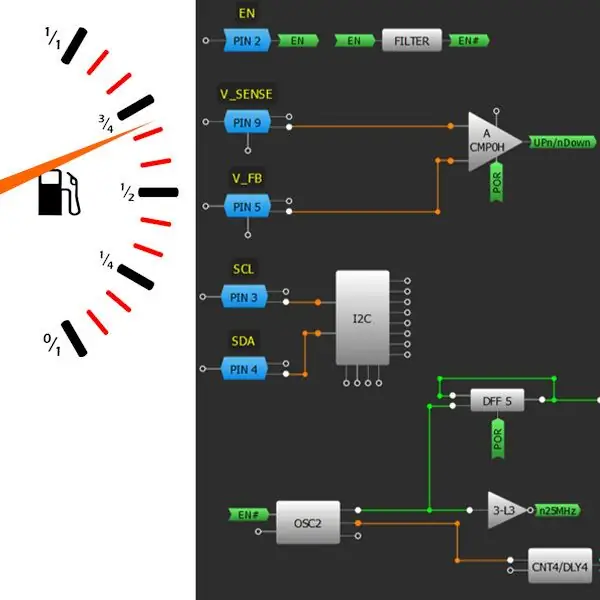

Korak 2: Unutarnji krug

Fleksibilni ADC temelji se na dizajnu predstavljenom u Dialog Semiconductor AN-1177. Takt se povećava s 1 MHz na 12,5 MHz radi taktiranja ADC brojača budući da SLG46855 ima na raspolaganju 25 MHz. To omogućuje mnogo bržu brzinu ažuriranja za bolju rezoluciju uzorka. LUT koji radi na ADC podatkovnom satu mijenja se tako da će prolaziti kroz signal od 12,5 MHz kada je PWM DFF nizak.

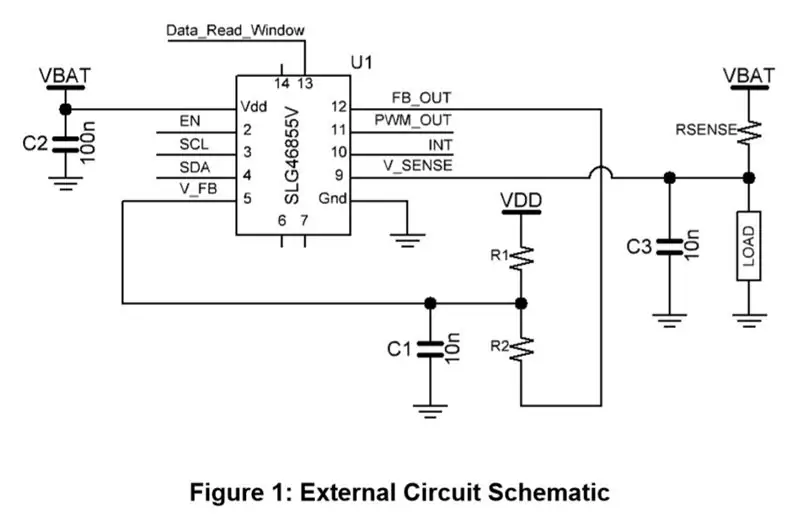

Korak 3: Vanjski krug

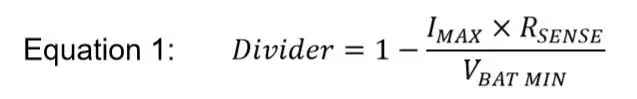

Vanjski otpornik i kondenzatorska mreža koriste se za pretvaranje PWM -a u analogni napon kako je prikazano na shemi sklopa na slici 1. Vrijednosti se izračunavaju za maksimalnu razlučivost za najveću struju koju će uređaj osjetiti. Da bismo postigli ovu fleksibilnost, dodamo otpornike R1 i R2 paralelno s VDD -om i masom. Razdjelnik otpornika dijeli VBAT na nisku stranu raspona napona. Omjer razdjelnika za očekivani minimalni VBAT može se riješiti pomoću jednadžbe 1.

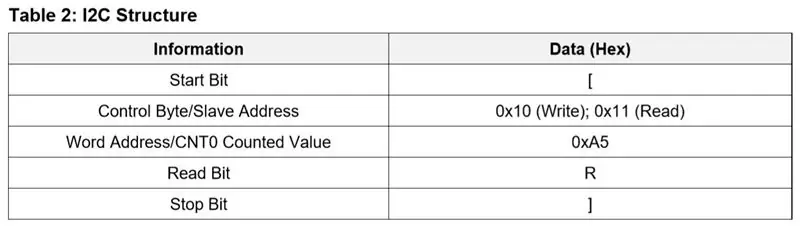

Korak 4: I2C Pročitajte upute

Tablica 1 opisuje strukturu naredbi I2C za čitanje podataka pohranjenih u CNT0. I2C naredbe zahtijevaju početni bit, kontrolni bajt, adresu riječi, bit za čitanje i bit za zaustavljanje.

Primjer I2C naredbe za očitavanje prebrojane vrijednosti CNT0 napisan je ispod:

[0x10 0xA5] [0x11 R]

Brojana vrijednost koja se ponovno čita bit će vrijednost ADC koda. Na primjer, Arduino kôd uključen je u ZIP datoteku ove bilješke o aplikaciji na web stranici Dialoga.

Korak 5: Rezultati

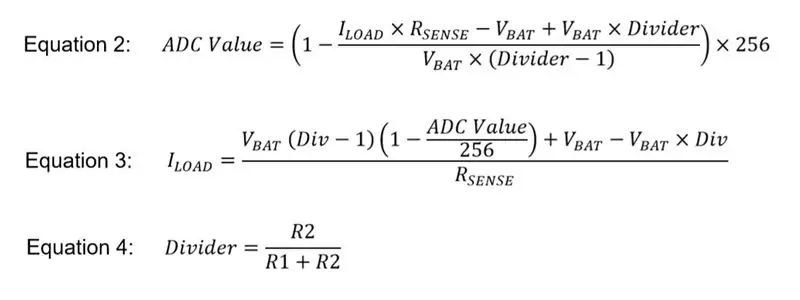

Kako bi se ispitala točnost dizajna osjetnika ADC struje, mjerene vrijednosti pri danoj struji opterećenja i razini VDD uspoređene su s teoretskom vrijednošću. Teoretske vrijednosti ADC -a izračunate su s jednadžbom 2.

ILOAD koji korelira s ADC vrijednošću nalazi se s jednadžbom 3.

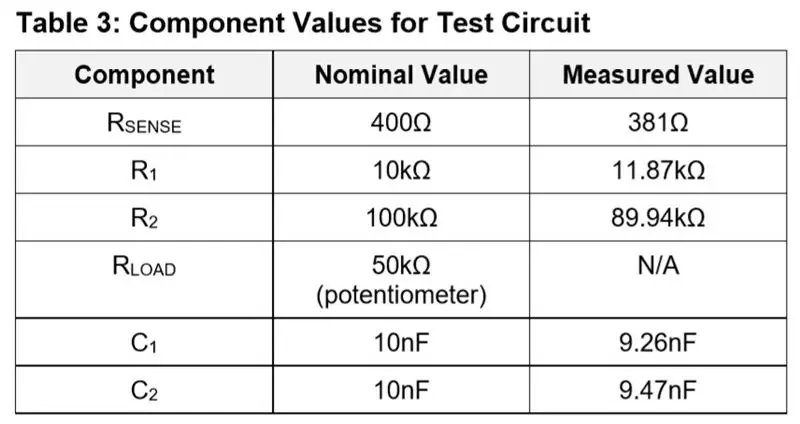

Za sljedeće rezultate koristio sam ove vrijednosti komponenata prikazane u tablici 3.

Razlučivost pretvorbe ADC vrijednosti u ILOAD može se izračunati pomoću jednadžbe 3 s izmjerenim vrijednostima u Tablici 2 i ADC vrijednosti postavljenom na 1. S VBAT od 3,9 V razlučivost je 4,96 µA/div.

Kako bi se strujni krug osjetnika ADC -a optimizirao na minimalnu razinu VDD -a od 3,6 V s maksimalnom strujom od 1100 µA i osjetnim otpornikom od 381 Ω, idealni koeficijent razdjelnika bio bi 0,884, na temelju jednadžbe 1. S vrijednostima navedenima u tablici 2, stvarni razdjelnik ima koeficijent razdjelnika 0,876. Budući da je to nešto manje, dopustit će nešto veći raspon struje opterećenja pa su vrijednosti ADC -a blizu punog raspona, ali se neće prelijevati. Stvarna vrijednost razdjelnika izračunava se jednadžbom 4.

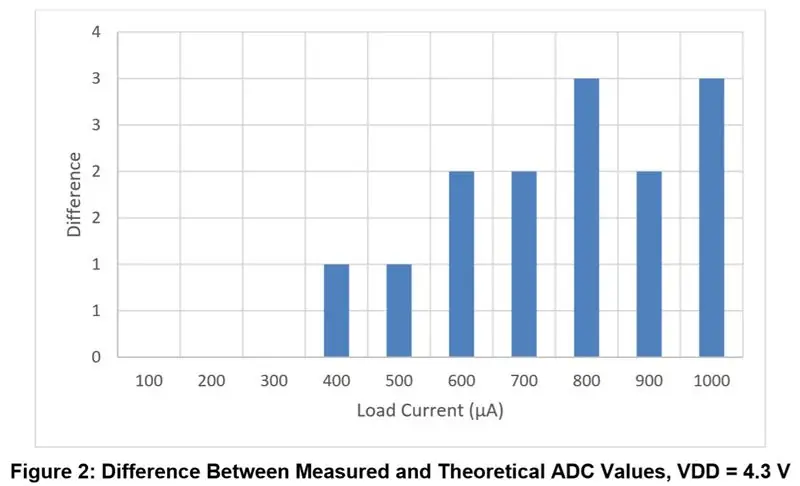

Gore (slike 2-6, tablice 4-6) su mjerenja izvedena u krugu na tri razine napona: 4,3 V, 3,9 V i 3,6 V. Svaka razina prikazuje grafikon koji prikazuje razliku između izmjerenih i teoretskih vrijednosti ADC-a. Teoretske vrijednosti zaokružene su na najbliži cijeli cijeli broj. Postoji zbirni grafikon za usporedbu razlika na tri razine napona. Nakon toga postoji grafikon koji prikazuje korelaciju između teoretskih vrijednosti ADC -a i struje opterećenja na različitim razinama napona.

Zaključak

Uređaj je testiran na tri razine napona: 3,6 V, 3,9 V i 4,3 V. Raspon ovih napona modelira punu litij -ionsku bateriju koja se prazni do nominalne razine. Od tri razine napona, uočeno je da je uređaj tipično bio točniji na 3,9 V za odabrani vanjski krug. Razlika između izmjerenih i teoretskih vrijednosti ADC -a bila je samo 1 decimalna vrijednost isključena pri strujama opterećenja od 700 - 1000 µA. U danom rasponu napona, izmjerene vrijednosti ADC -a bile su za 3 decimalne točke iznad nominalnih uvjeta u najgorem slučaju. Daljnje prilagodbe razdjelnika otpornika mogu se izvršiti radi optimizacije različitih razina napona VDD.

Preporučeni:

Žarulja za osjet zvuka: 5 koraka

Zvučna žarulja: Dizajn je planiranje i razmišljanje o stvaranju nečega. Projekt koji dolazi iz vaše mašte i čini ga stvarnim. Prilikom projektiranja morate biti sigurni da znate što je dizajnersko razmišljanje. Dizajnersko razmišljanje je način na koji sve planirate unaprijed. Za

Trenutni izvor DAC AD5420 i Arduino: 4 koraka (sa slikama)

Trenutni izvor DAC AD5420 i Arduino: Pozdrav. U ovom članku želio bih podijeliti svoje iskustvo s trenutnim digitalno-analognim pretvaračem AD5420, koji ima sljedeće karakteristike: 16-bitna razlučivost i monotonostTrenutni izlazni rasponi: 4 mA do 20 mA, 0 mA do 20 mA, ili 0 mA t

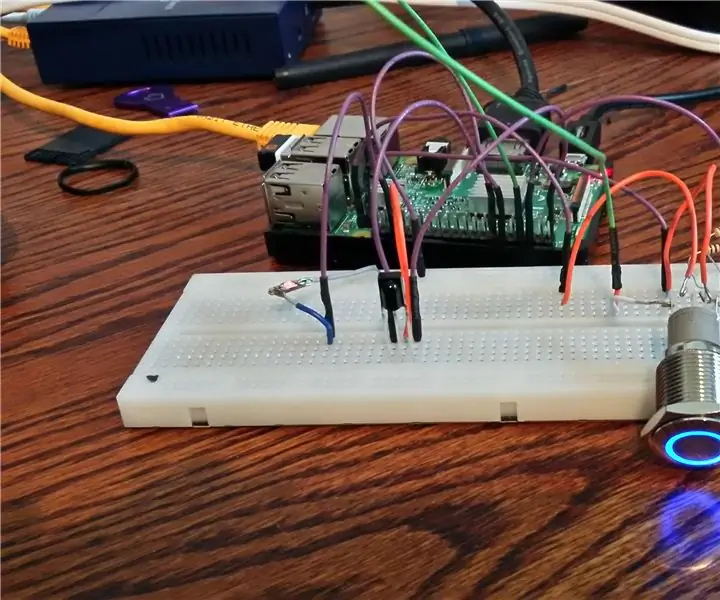

Dodajte trenutni prekidač Adafruit's Ring LED u Raspberry Pi: 3 koraka (sa slikama)

Dodajte trenutni prekidač Adafruit's Ring LED za Raspberry Pi: Kao dio svog sustava za rezanje kabela, želim indikator napajanja i prekidač za resetiranje na medijskom centru sa Raspberry Pi-om koji radi pod Kodijem na OSMC-u. Pokušao sam nekoliko različitih trenutnih prekidača. Adafruit -ovo robusno metalno dugme s plavim LED -om jako je cool

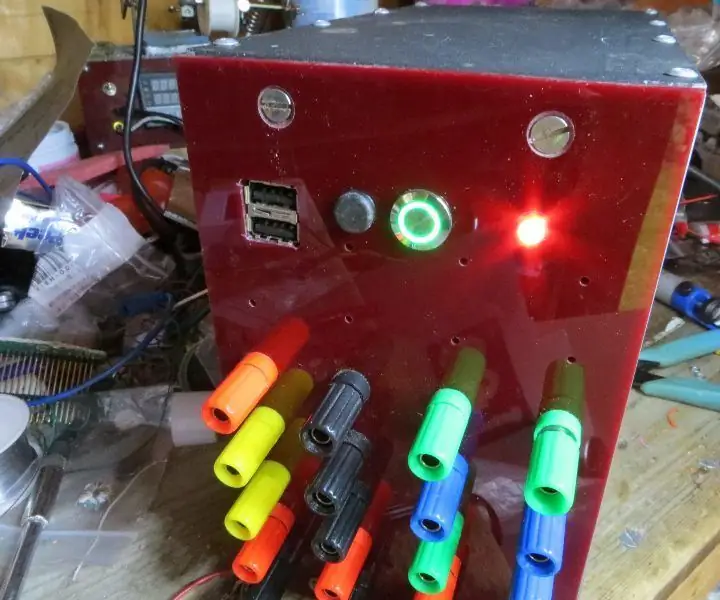

Odgovarajući trenutni prekidač za pretvorbu ATX PSU: 4 koraka

Odgovarajući trenutni prekidač za pretvorbu ATX PSU: što? Čujem kako govoriš! Trenutni prekidač koji se zaključava? tako nešto zasigurno nije moguće! Ali jest. Našao sam dizajn na netu i malo ga prilagodio tako da će se, ako je spojen na ATX psu, prebaciti na ispravnu postavku ako se PSU isključi

Utičnica s pokretom - sa svjetla za osjet kretanja: 6 koraka

Utičnica s pokretom - sa svjetla osjetljivog na kretanje: Zamislite da ste prevarant i idete u najstrašniju kuću u bloku. Nakon što prođete sve duhove, duhove i groblja konačno dolazite do posljednje staze. Možete vidjeti slatkiše u zdjeli ispred vas! Ali onda odjednom gho